🎉 Exclusive offer: FREE shipping of all MCU & MPU products. No code or minimum required. 🛒 Order now!

📢 Bonus offer: Get our latest VIPGAN65 board with Free shipping. Use code DV-EVLVIPGAN65DF-FREESHIP-05 at checkout! 🛒 Claim now!

Active

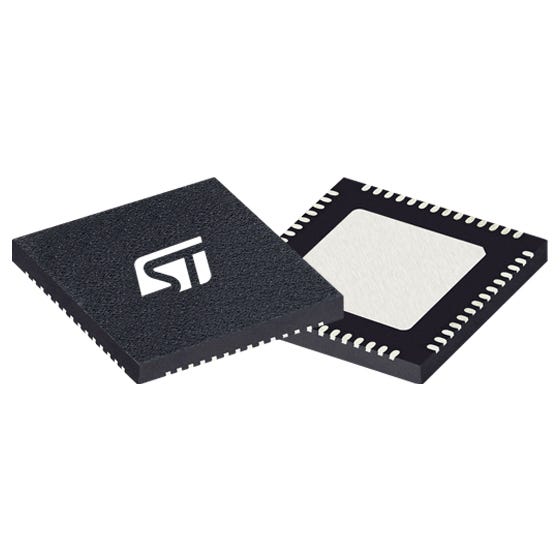

ST8500TR

Programmable power-line communication modem system-on-chip

| ECCN US | 5A992.c |

| ECCN EU | 5A002.a.2 |

| Packing Type | Tape And Reel |

| RoHs compliant | Ecopack2 |

| Grade | Industrial |

| Package Name | VFQFPN 56 7x7x1.0 |

The ST8500 is a fully programmable power-line communication (PLC) modem system-on-chip (SoC), which is able to run any PLC protocol in the frequency band up to 500 kHz. The device architecture has been designed to target CENELEC EN50065, FCC and ARIB compliant applications supporting all major PLC...

Read More

|

| Quantity | $ per unit | Savings |

|---|---|---|

| 1-9 | $10.77 | 0% |

| 10-24 | $8.46 | 21% |

| 25-99 | $7.99 | 26% |

| 100-249 | $7.31 | 32% |

| 250-499 | $7.07 | 34% |

| 500 | $6.73 | 37% |

| 500 + |

Contact sales |

|

| ECCN US | 5A992.c |

| ECCN EU | 5A002.a.2 |

| Packing Type | Tape And Reel |

| RoHs compliant | Ecopack2 |

| Grade | Industrial |

| Package Name | VFQFPN 56 7x7x1.0 |

The ST8500 is a fully programmable power-line communication (PLC) modem system-on-chip (SoC), which is able to run any PLC protocol in the frequency band up to 500 kHz. The device architecture has been designed to target CENELEC EN50065, FCC and ARIB compliant applications supporting all major PLC...

Read More

|